Task 4: Complementary projects

Task Responsible: Jorge Sousa

Sub-Tasks

4.1. ATCA PCIe switch Firmware - White Rabit Implementation

2012-01-09 The architecture of the firmware is now defined. An issue still exists regarding the availability of the WR PTP control software (not found on the WR SVN repository)

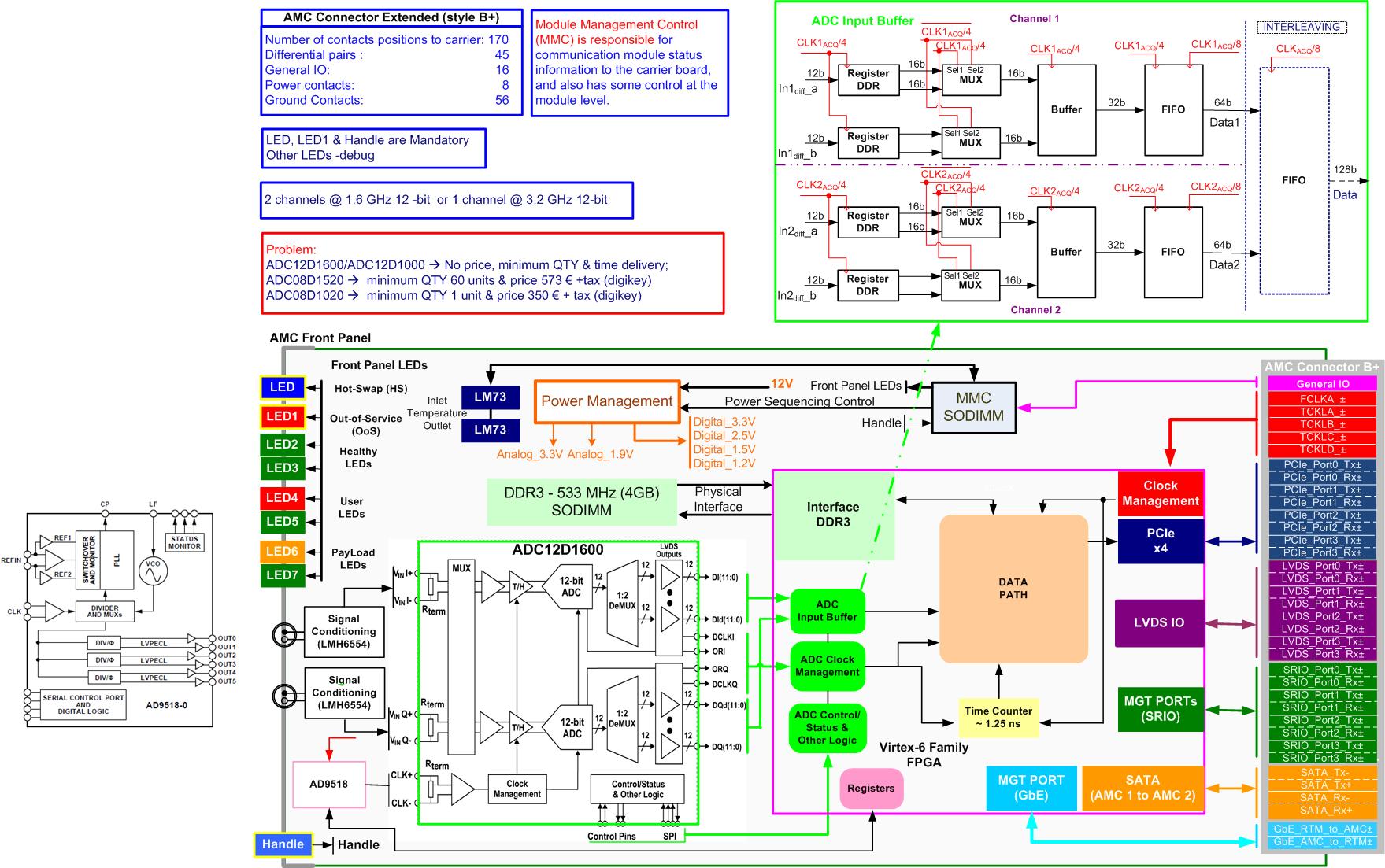

4.2. AMC Card (3 GSPS)

2012-01-09 The preliminary architecture of the card and FPGA code in now defined. Component assessment in progress.

4.3. ADC (10 MSPS)

2012-01-02 An assessment of the available 16-bit 10 MSPS serial ADCs from various manufacturers, found the more adequate ADC for this module (in terms of static and dynamic parameters, latency and footprint area) to be the Analog Devices AD7626 as well as the pin-to-pin compatible AD7625 (up to 6 MSPS for lower sampling frequency, lower cost requirements).

4.4 RTM with PCIe over Optical Fiber for the ATCA PCIe Switch card

2012-01-09 No activities were performed yet.

4.5. Position Reflectometry - case study

To use the ITER prototype fast plant system controller for the development of the plasma position reflectometry case study for the data acquisition and algorithms

4.6. AMC Card (100 MSPS+)

Relevant for MW diagnostics on several existing tokamaks

4.7. Digital Integrator

Digital Integrator based on the chopper ADC module for the ATCA-IO-PROCESSOR test-bench.

Tests shall assess the performance for long term integration.